0 引言

晶体振荡器的老化漂移是影响晶体振荡器频率稳定度和准确度的重要原因之一。

10MHz晶体振荡器(以下简称“OCXO”)在长期使用后,输出频率会偏离标称值(频率漂移),有可能无法满足通信设备指标要求。因此,当OCXO频率产生漂移时,需要对其进行校准。

自动频率校准晶体振荡器单元采用全数字处理方式,通过对高精度10MHz参考频率源和OCXO输出频率的测量、比对、计算,产生数字调谐电压,对OCXO输出频率进行调整,当OCXO输出频率与高精度10MHz参考频率源经比对满足指标要求后,自动停止调谐,并将此电压存储到存储器中,待下次开机上电后读入,确保OCXO保持上一次校准后的频率值。

1 方案设计

1.1 单元架构

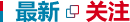

自动频率校准晶体振荡器单元主要由OCXO和频率校准两部分组成。频率校准部分包括FPGA、TDC-GP21、DAC、FLASH等IC类器件及外围电路。单元组成示意图如图1所示。

图1 单元组成示意图

1.2 频率校准原理

频率校准过程是一个比对过程,以RF-10MHz为基准,通过调整OCXO输出频率,使其输出频率与RF-10MHz的输出频率逐步接近,由于RF-10MHz的频率精度比OCXO高两个数量级,当两者没有频率差时,OCXO频率的精度就达到RF-10MHz的精度。基于此原理,当两者频率差小于一定值时,OCXO输出频率就能达到一定精度,达到了频率校准目的。

说明:RF-10MHz和OCXO必须工作稳定后,才能进行频率校准。

1.3 自动频率校准工作流程

自动频率校准晶体振荡器单元加电,当有外部“RF-10MHz”接入时,“检测模块”(detect)对外接信号进行粗略的频率反测,当“RF-10MHz”频率精度达到±5E-7量级,认定“RF-10MHz”为可用的参考信号,点亮模块上的信号检测LED。同时,“延时模块”(delay),自动延时5分钟,保证OCXO输出稳定。

在以上两个条件满足要求后,FPGA下发指令开启TDC-GP21的测量部分,TDC-GP21的测量数据读入FPGA,通过FPGA内部计算将测量的相位差转换为两信号的频率差。根据计算出的两信号频率差值以及OCXO频率与压控电压的经验数据,通过DAC调整、改变OCXO的压控电压,进而校准OCXO的频率。

通过反复的测量、比对、调整循环,确保OCXO的输出频率在要求的校准精度内。

2 频率校准部分设计

2.1 测量单元

要实现对OCXO频率的校准,首先需要对OCXO输出信号和RF_10MHz的输入信号相位差进行高精度测量。为保证测量精度,选用通用双通道时间数字转换器TDC-GP21来完成测量工作。

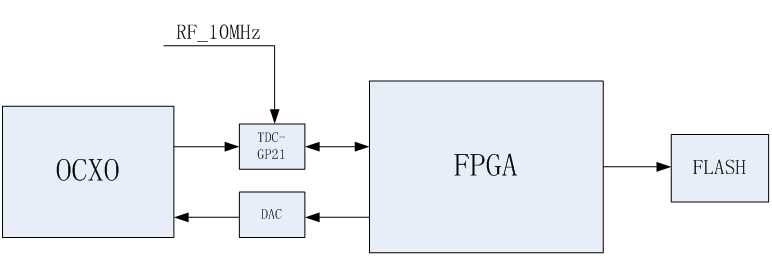

整个测量过程,由FPGA指令控制,测量时序如图2所示。当TDC-GP21芯片接收到FPGA发送来的测量触发信号后,开始对start信号以及stop信号进行检测。

测量单元由start信号触发工作,收到stop信号后停止工作。由环形振荡器的位置和粗值计数器的计数值可以计算出start信号和stop信号之间时间间隔,测量范围可达20位。

图2 测量时序图

TDC的高速测量单元并不测量整个时间间隔,仅仅测量从start或stop信号到相邻的基准时钟上升沿之间的间隔时间(fine-counts),即图2中的Finecount1和Finecount2。在两次精密测量之间,TDC记下基准时钟的周期数(coarse-count)。最后,TDC测量1个和2个参考时钟周期,这两个数据作为Cal1和Cal2存储起来,用于校准测量。测量结束,TDC-GP21对测量结果进行数据处理,并将结果RES_X送入输出寄存器,FPGA收到TDC-GP21返回的中断信号,并向TDC-GP21再次发送读取指令,读取TDC-GP21输出寄存器中的测量结果RES_X,测量过程结束。

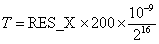

start信号上升沿和stop信号上升沿之间的时间间隔T(即两信号间的相位差time)可以通过公式(1)计算得到:

(1)

(1)

2.2 信号处理单元

由于FPGA是边沿触发,因此需要对“RF-10MHz”和OCXO的输出波形进行处理,将输出的正弦波信号转换为方波信号,作为FPGA的边沿触发时钟信号。

为了提高测量精度,利用FPGA将OCXO的10MHz信号和“RF-10MHz”信号分频到1pps脉冲信号。

测量芯片TDC-GP21测量方式2的量程为0~4ms,因此需要保证两被测信号(图2中start信号和stop信号)上升沿之间的相位差在此量程中。通过FPGA严格的时序控制,将这两个1pps信号的相位差设置在2ms附近,以保证在TDC测量时使用量程的中间区域,避免出现负值导致测量的溢出。

2.3 频率校准单元

要实现对OCXO频率的校准,就需要确定OCXO与“RF-10MHz”的频率差,根据计算出的频率差值以及OCXO频率与压控电压的关系,通过DAC来改变OCXO的压控电压,调整OCXO频率。

通过反复的测量、比对、调整循环,确保OCXO的输出频率达到要求的校准精度。

2.3.1 计算频率差

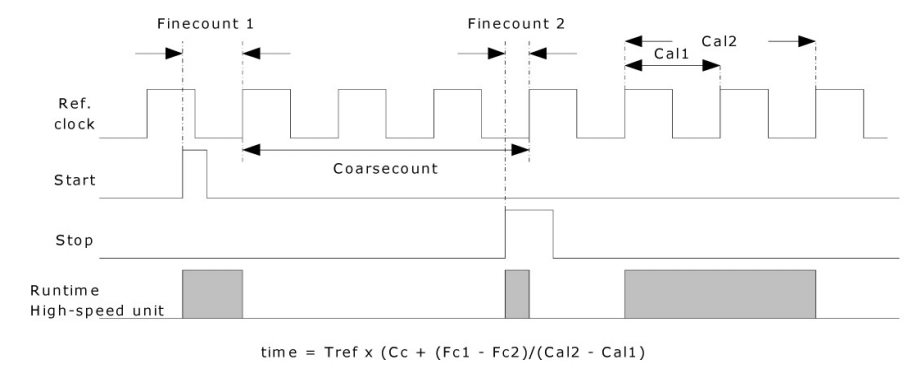

根据相位差计算公式T=RES_X*Tref*N;代入设计参数得到公式(2):

(2)

(2)

其中,Tref是TDC-GP21参考时钟的周期,这里采用5MHz的参考时钟,即Tref为200ns;N为测量设置中的内部基准时钟的分频数,这里采取不分频的方式,即N为1。

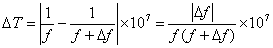

设start信号的频率为f,start信号与stop信号之间的频差为Δf。当测量周期为1s时,连续两次测量的相位差之间的差值可以表示为:

(3)

(3)

根据OCXO的压控调整范围可知,Δf与f相差在6个数量级左右,因此公式(3)可以简化为:

(4)

(4)

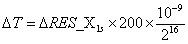

由公式(2)可知,测量周期为1s时连续两次测量的相位差之间的差值可以表示为:

(5)

(5)

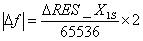

其中,DRESx1s为测量周期1s时联系两次测量读回TDC-GP21的测量值RES_X的差值。结合公式(4)和公式(5),并将107代入f,等式可以写作:

(6)

(6)

至此,根据公式(6)即可根据连续两次的测量差值DRESx1s转换为所需要的频差。

2.3.2 频率校准的实现

计算出频率差后,要使OCXO频率达到要求的精度,就需要对OCXO压控电压值进行设计,以保证OCXO压控电压的调整精度。

根据OCXO的压宽范围属性,选取了16位调整精度的DAC器件,保证了对OCXO压控电压的调整精度,进而保证了OCXO的频率校准精度。

采用电压基准REF3230对DAC器件提供供电和参考电压,REF3230良好的电压稳定性保证了OCXO压控电压的稳定性,有效地提高了校准精度。

根据计算出的频率差值以及OCXO频率值与压控电压的经验数据,通过FPGA向DAC写入数据,通过DAC调整、改变OCXO的压控电压,进而校准OCXO的频率。通过反复的测量、调整循环,确保OCXO的输出信号频率在要求的校准精度内。当频率精度进入±5E-10后,停止DAC的调整工作,并判定为锁定状态,点亮模块上的锁定指示LED。

3 达到的指标

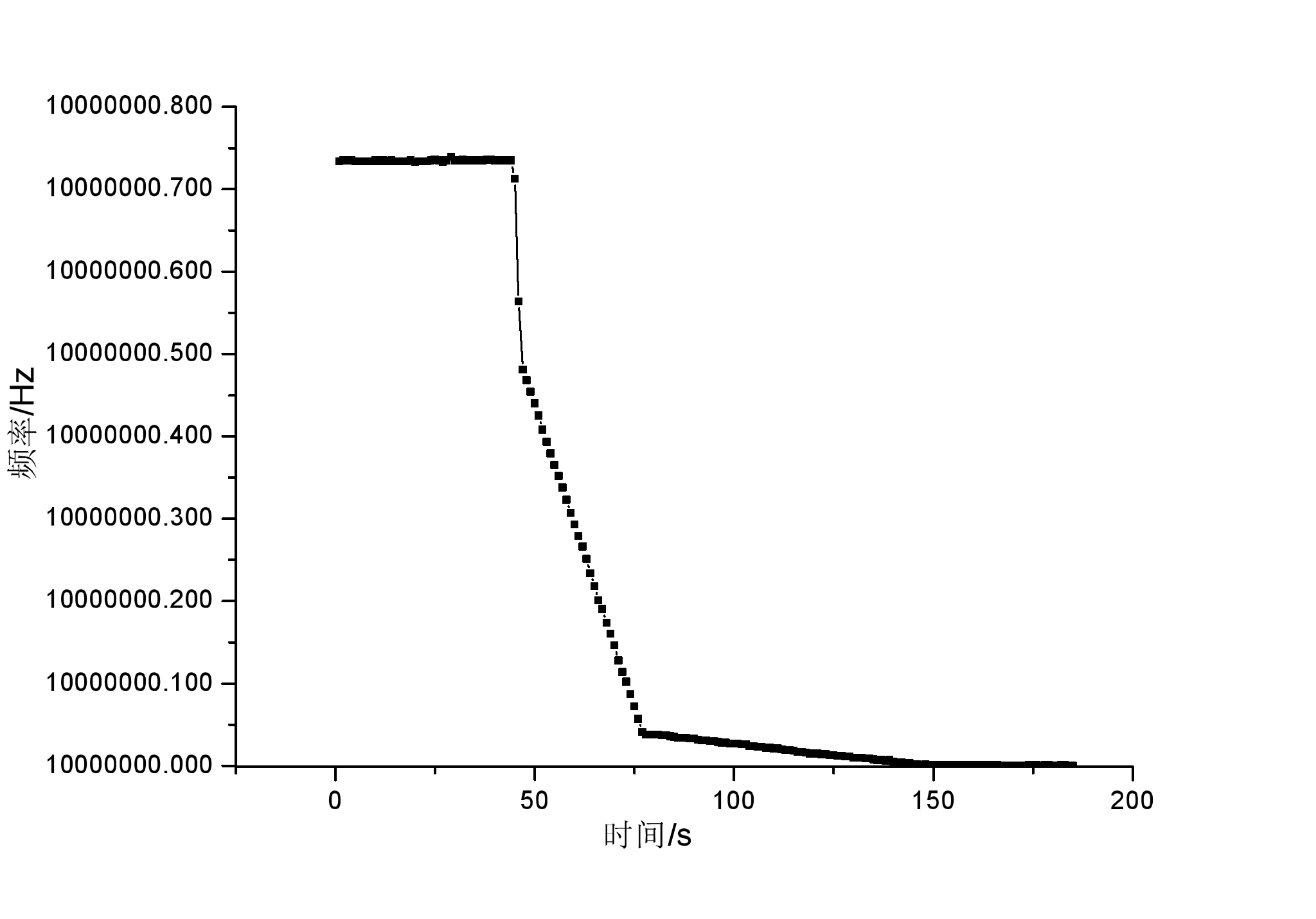

时钟模块的实际校准过程频率采样数据如图3所示。校准前OCXO的频率为10000000.735Hz,校准完成后,OCXO的频率为10000000.001Hz,整个校准过程大约持续2min左右。校准精度为±5E-10。

图3 采样数据图

4 结论

具有自动频率校准功能的晶体振荡器单元在不需要专业仪器情况下,通过数据处理方式就能实现对频率的自动校准,改进了传统频率校准方式,提高了频率校准精度,建立了一种新型频率校准方法。

通过对晶振频率偏移的自动测量以及对晶振压控端电压的自动控制,使得校频后的晶振老化得到了明显的抑制,校准后的晶振准确度明显优于校准前的准确度。

该系统采用实用方便的方法达到了将晶体振荡器校准到较高指标的目的。

参考文献

[1]孙成城.高稳定度晶体振荡器的低老化率及补偿问题研究[D].西安:西安电子科技大学,2013.

(作者系中国电子科技集团公司第五十四研究所高级工程师)